# **VGA Controller v1.2**

#### **IP** Documentation

November 2021

VGA Controller v1.2

Page 1 | 13

# **Licensing Notice**

**VGA Controller v1.2** is a fully tested, portable, configurable, and synthesisable soft IP core provided by **Chip**munk **Logic**<sup>™</sup>. The IP source files are complied with IEEE VHDL/Verilog/System-Verilog standards. All the source codes are open-source licensed and hence may be used, modified, and shared without any restrictions or conflicts of interest with the original developer.

**Chip**munk **Logic**<sup>™</sup> shall not be liable or held accountable for any loss or damage (direct or indirect) resulting from the use of any product, as the designs are not intended to be fail-safe or for use in any application requiring fail-safe performance. Hence, the user shall assume sole risk and liability for the use of any of our products in any of their applications.

# **Table of Contents**

| 1. VGA Controller |                             | A Controller                                 | 4  |  |  |  |

|-------------------|-----------------------------|----------------------------------------------|----|--|--|--|

| 2.                | Features4                   |                                              |    |  |  |  |

| 3. Overview       |                             |                                              |    |  |  |  |

| 4.                | Video Timing6               |                                              |    |  |  |  |

| 5.                | . Configuration Parameters7 |                                              |    |  |  |  |

| 6.                | Top-level Ports/Interfaces  |                                              |    |  |  |  |

| 7.                | Des                         | Designing with the IP9                       |    |  |  |  |

| 7                 | .1                          | Clocking                                     | 9  |  |  |  |

| 7                 | .2                          | Reset                                        | 9  |  |  |  |

| 7                 | .3                          | Configuring the IP                           | 9  |  |  |  |

| 7                 | .4                          | Frame Synchronization                        | 9  |  |  |  |

| 7                 | .5                          | Clock Enable to control pixel rate           | 10 |  |  |  |

| 8.                | Арр                         | pendix                                       | 11 |  |  |  |

| 8                 | .1                          | Example Design and Testing                   | 11 |  |  |  |

| 8                 | .2                          | Performance and Resource Utilization on FPGA | 12 |  |  |  |

## 1. VGA Controller

VGA Controller is a soft IP core to generate video timing signals to facilitate driving VGA/DVI Monitors of a wide range of resolutions and timing requirements. The IP is dynamically configurable for real-time video timing signals generation.

## 2. Features

- ✓ Supports clocked progressive videos.

- ✓ Configurability:

- Max. resolution compile-time configurable

- o Resolution, active, blanking, sync, and sync pulse polarity run-time configurable

- $\checkmark$  Supports standard as well as custom video resolutions.

- ✓ Supports synchronizing the core operation with an external frame sync pulse.

- ✓ Timing complied with <u>VESA monitor standard</u>.

## 3. Overview

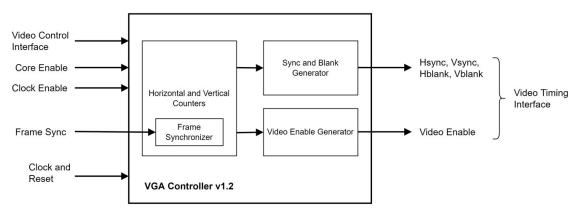

VGA Controller generates video timing based on the current configuration. Figure 3.1 shows the functional block diagram of the core.

Figure 3.1: VGA Controller – Block Diagram

The core has two primary interfaces.

- Video Control Interface: This interface is used to control/configure the core at runtime. It consists of active, blanking, sync, and polarity configuration signals. These signals can be tied to constant, to use the core as a static IP to drive a specific video resolution.

- **Video Timing Interface**: This interface drives the display. It generates all video timing signals as derived from the current configuration.

## 4. Video Timing

The core can support all standard resolutions as well as custom resolutions configured by user at run-time. Once the core is configured and enabled, video timing signals are generated automatically. The core doesn't require any user intervention thereafter; unless the user wants to change the video resolution.

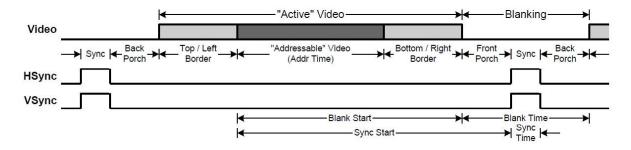

All timing signals generated are in compliance with <u>VESA monitor standard</u>. Fig 4.1 shows sample video timing for active-high Hsync and Vsync signals.

Fig 4.1: Video Timing

# 5. Configuration Parameters

The core supports compile-time configuration of maximum video resolution supported. Higher the value, more the resource utilization. The resource utilization can thus be controlled/limited as per the requirements of the user using this parameter. Table 4.1 lists all configuration parameters available to the user.

| Parameter   | Туре    | Default | Description                                                  |

|-------------|---------|---------|--------------------------------------------------------------|

| MAX_FWIDTH  | integer | 1920    | Maximum frame width, including blanking.<br>Min. value = 16  |

| MAX_FHEIGHT | integer | 1080    | Maximum frame height, including blanking.<br>Min. value = 16 |

Table 5.1: Configuration Parameters

# 6. Top-level Ports/Interfaces

Table 5.1 lists all top-level I/O ports/interfaces of VGA Controller.

| Signal Name             | Direction | Width                                | Description                                                                                         |  |  |  |  |

|-------------------------|-----------|--------------------------------------|-----------------------------------------------------------------------------------------------------|--|--|--|--|

| clk                     | input     | 1                                    | Core Clock                                                                                          |  |  |  |  |

| rst                     | input     | 1                                    | Core Reset; synchronous, active-high                                                                |  |  |  |  |

| i_clk_en                | input     | 1                                    | Clock Enable. Refer <u>here</u> for more details.                                                   |  |  |  |  |

| i_core_en               | input     | 1                                    | Core Enable; enables the IP to generate video timing.                                               |  |  |  |  |

| i_fsync                 | input     | 1                                    | Frame Sync pulse to synchronize the generation of video timing. Refer <u>here</u> for more details. |  |  |  |  |

| Video Control Interface |           |                                      |                                                                                                     |  |  |  |  |

| i_hsync_pol             | input     | 1                                    | Horizontal Sync polarity                                                                            |  |  |  |  |

| i_vsync_pol             | input     | 1                                    | Vertical Sync polarity                                                                              |  |  |  |  |

| i_hdisp                 | input     | ceil(log2(MAX_FWIDTH))               | Active Video width                                                                                  |  |  |  |  |

| i_hfront                | input     | ceil(log2(MAX_FWIDTH))               | Horizontal Front Porch                                                                              |  |  |  |  |

| i_hsync_len             | input     | ceil(log2(MAX_FWIDTH))               | Horizontal Sync pulse width                                                                         |  |  |  |  |

| i_hback                 | input     | <pre>ceil(log2(MAX_FWIDTH))</pre>    | Horizontal Back Porch                                                                               |  |  |  |  |

| i_vdisp                 | input     | ceil(log <sub>2</sub> (MAX_FHEIGHT)) | Active Video height                                                                                 |  |  |  |  |

| i_vfront                | input     | ceil(log <sub>2</sub> (MAX_FHEIGHT)) | Vertical Front Porch                                                                                |  |  |  |  |

| i_vsync_len             | input     | ceil(log <sub>2</sub> (MAX_FHEIGHT)) | Vertical Sync pulse width                                                                           |  |  |  |  |

| i_vback                 | input     | ceil(log <sub>2</sub> (MAX_FHEIGHT)) | Vertical Back Porch                                                                                 |  |  |  |  |

| Video Timing Interface  |           |                                      |                                                                                                     |  |  |  |  |

| o_data_en               | output    | 1                                    | Video Enable                                                                                        |  |  |  |  |

| o_hblank                | output    | 1                                    | Horizontal Blank                                                                                    |  |  |  |  |

| o_hsync                 | output    | 1                                    | Horizontal Sync                                                                                     |  |  |  |  |

| o_vblank                | output    | 1                                    | Vertical Blank                                                                                      |  |  |  |  |

| o_vsync                 | output    | 1                                    | Vertical Sync                                                                                       |  |  |  |  |

|                         |           | 1                                    |                                                                                                     |  |  |  |  |

Table 6.1: Top-level I/O Ports/Interfaces

## 7. Designing with the IP

This chapter discusses the guidelines, performance, and other known limitations while designing with VGA Controller.

## 7.1 Clocking

The core has a single clock. The clock should be faster or equal to the pixel rate required. Refer to <u>VESA monitor standard</u> for pixel rates required for different resolutions and refresh rates.

### 7.2 Reset

The external reset should be synchronous to clock. Single cycle pulse is enough to reset the core.

## 7.3 Configuring the IP

The IP is configurable at run-time via *Video Control Interface*. The core provides frame-byframe control. All control signals at *Video Control Interface* are buffered to ensure that no intraframe artifacts/mistiming occur if the configuration is modified by user while a frame is being rendered by the core. Recommended sequencing for configuring the IP is:

- 1. Reset the IP.

- 2. Configure all necessary control signals at Video Control Interface.

- 3. Set Core Enable to 'high'.

- 4. If required, pulse i\_fsync to start generating timing in synchronization with this pulse.

## 7.4 Frame Synchronization

The core's operation can be synchronized with external frame sync pulse at i\_fsync at any point of time. On asserting this signal, the core resets all its counters. The core starts regenerating video timing once i\_fsync is de-asserted.

The core re-generates timing based on the current configuration. IP configuration is buffered every frame; hence the timing for new configuration may be generated only after a frame latency in the worst case.

If low-latency operation is required after the IP configuration, i\_fsync can be pulsed at the beginning. The signal i\_fsync need to be pulsed only for one clock cycle. If this signal is unused, it should be tied to 'low'.

#### 7.5 Clock Enable to control pixel rate

Clock Enable signal can be used to control pixel rate. This signal has to be asserted for normal operation. De-asserting this signal will stall the core's operation. Clock Enable can be used to control pixel rate in case Core Clock is faster than pixel rate required.

If Core Clock is faster than pixel rate, Clock Enable can be pulsed at appropriate intervals to generate video timing at pixel rate. Clock Enable is then oversampled by Core Clock to generate video timing. This is equivalent to clocking the core at pixel rate. However, user should take into consideration how accurate the derived pixel rate is after oversampling.

If Core Clock is same as pixel rate, then Clock Enable can be simply tied to 'high'.

# 8. Appendix

### 8.1 Example Design and Testing

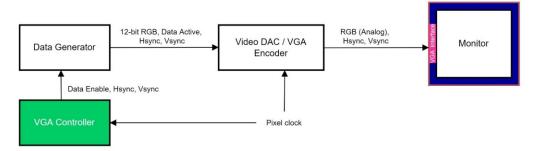

The IP comes with two synthesisable example designs to test a VGA Controller based video system on board. There are two example designs provided for testing:

- Module *video\_top\_clken* to test VGA Controller with Clock Enable to control pixel rate. This is portable RTL across all platforms to test any video resolution as configured by user. Simple color pattern is tested. By default, 640 x 480p is tested.

- Module *video\_top\_pll* to test VGA Controller with PLL to generate pixel clock from an external system clock. This is compatible with designs that instantiate PLL, and can be configured to any video resolution. Simple color pattern in background with moving text is tested. By default, 1280 x 720p HD is tested.

The test framework is shown in Fig 8.1. The 12-bit RGB digital output can be interfaced to any VGA/DVI compatible display through a Video DAC like ADV7125 / Simple Resistor-network DAC / RGB Encoder IC to view the video.

Fig 8.1: VGA Controller On-board Testing

#### 8.2 Performance and Resource Utilization on FPGA

The following is an estimate of timing and resource utilization of *VGA Controller v1.2* configured to support up to 1920 x 1080p Full HD when targeted on Xilinx Artix-7 FPGA.

| IP Configuration            | MAX_FWIDTH = 2048<br>MAX_FHEIGHT = 2048   |

|-----------------------------|-------------------------------------------|

| FPGA Targeted               | Xilinx Basys-3 Board (XC7A-35T-CPG236-1)  |

| Synthesiser                 | Vivado 2018.3                             |

| Targeted Clock<br>Frequency | 148.5 MHz, timing verified up to 200 MHz. |

| LUTs                        | 133                                       |

| Registers                   | 131                                       |

# VGA Controller v1.2

An open-source licensed IP core

#### Developer : Mitu Raj

Vendor : Chipmunk Logic<sup>™</sup>, chip@chipmunklogic.com

Website : chipmunklogic.com